# TECHNOLOGIE DES CIRCUITS LOGIQUES

# I. APPPORT DE CONNAISSANCES

Les circuits intégrés logiques sont classés suivant leur technologie de fabrication (bipolaire TTL, bipolaire ECL, MOS,...). Pour un fonctionnement logique identique, chaque technologie offre des performances différentes sur le plan électrique (tensions, courants, puissances) et temporel (rapidité).

Rappel: Lorsque l'on travaille avec des circuits logiques deux états sont considérés: l'état haut et l'état bas. Ces deux états sont définis par des plages de tensions en fonction de la technologie utilisée. En logique positive l'état haut correspond à une présence de tension et à un « 1 » logique.

Une famille logique est caractérisée par ses paramètres électriques :

- la plage des tensions d'alimentation et la tolérance admise sur cette valeur,

- la plage des tensions associée à un niveau logique, en entrée ou en sortie,

- les courants pour chaque niveau logique, en entrée ou en sortie,

- le courant maximum que l'on peut extraire d'une porte logique et le courant absorbé en entrée,

- la puissance maximale consommée qui dépend souvent de la fréquence de fonctionnement. Les performances dynamiques principales sont :

- les temps de montée (transition bas-haut) et de descente (transition haut-bas) des signaux en sortie d'une porte,

- les temps de propagation d'un signal entre l'entrée et la sortie d'une porte logique.

### Paramètres caractéristiques :

V<sub>cc</sub> - tension d'alimentation : niveau de tension nécessaire pour alimenter le circuit.

V<sub>IH</sub> (min) - tension d'entrée niveau HAUT : niveau de tension nécessaire pour avoir un 1 logique en entrée.

V<sub>IL</sub> (max) - tension d'entrée niveau BAS : niveau de tension nécessaire pour avoir un 0 logique en entrée.

V<sub>OH</sub> (min) - tension de sortie niveau HAUT : niveau de tension de la sortie d'un circuit logique correspondant à l'état logique 1.

V<sub>oL</sub> (max) - tension de sortie niveau BAS : niveau de tension de la sortie d'un circuit logique correspondant à l'état logique 0.

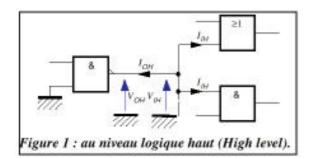

I<sub>IH</sub> - courant d'entrée niveau HAUT : le courant qui traverse une borne d'entrée quand une tension niveau haut est appliquée à cette entrée.

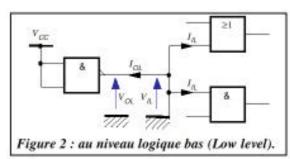

**I**<sub>IL</sub> - **courant d'entrée niveau BAS** : le courant qui traverse une borne d'entrée quand une tension niveau bas est appliquée à cette entrée.

**I**<sub>OH</sub> - **courant de sortie niveau HAUT** : le courant qui traverse une borne de sortie placée au niveau logique 1 dans des conditions de charge spécifiées.

**I**<sub>OL</sub> - **courant de sortie niveau BAS** : le courant qui traverse une borne de sortie placée au niveau logique 0 dans des conditions de charge spécifiées.

<u>Sortance</u>: Normalement, la sortie d'un sortie logique doit pouvoir piloter plusieurs entrées logiques. La *sortance* (appelée également *facteur de charge*) est définie comme le nombre *maximal* d'entrées logiques standards qui peuvent être pilotées sans problèmes par une sortie. Par exemple, quand il est indiqué qu'une porte logique a une sortance de 10, cela signifie qu'elle peut piloter 10 entrées logiques standards. Si on dépasse ce nombre, il n'est pas assuré que les tensions des niveaux logiques des sorties seront exactes.

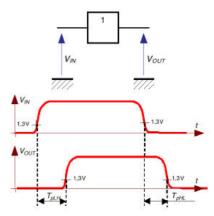

<u>Retards de propagation :</u> Un signal logique qui traverse un circuit subit toujours un retard.

Deux retards de propagation sont définis :

t<sub>PHL</sub>: retard pour passer du niveau logique 1 au niveau logique 0. t<sub>PHL</sub>: retard pour passer du niveau logique 0 au niveau logique 1.

<u>L'immunité au bruit</u>: Un bruit est une variation intempestive (ou aléatoire) d'une grandeur physique autour de la valeur déterminée (permanente, attendue ou nominale).

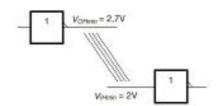

L'immunité au bruit est la marge de sécurité que l'on peut observer sans provoquer un changement d'état logique non désiré : c'est l'amplitude maximale du signal parasite à superposer au signal d'entrée pour provoquer un changement d'état en sortie.

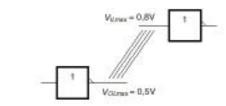

Marge de sensibilité aux bruits état haut :

$$V_{NH} = V_{OH(min)} - V_{IH(min)}$$

Marge de sensibilité aux bruits état bas :

$$V_{NL} = V_{OL(max)} - V_{IL(max)}$$

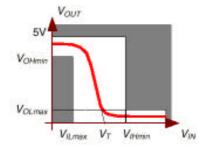

# Gabarit de transfert :

Il décrit les seuils haut et bas, d'entrée et de sortie d'un circuit logique.

Une porte satisfait le *gabarit* si sa courbe de transfert se trouve dans la partie non grisée.

La **tension de basculement**, notée  $V_T$  (T pour *threshold*, seuil), correspond à la tension d'entrée pour

laquelle la sortie change d'état.

# Complément d'informations sur le technologies :

C'est la référence du circuit qui détermine sa technologie.

<u>Les circuits TTL</u>: Dans cette série 10 familles sont disponibles : **7 en technologie TTL**, logique à transistors bipolaires et **3 en technologie CMOS (Complementary MOS)**

- TTL Standard 74xx TTL Low power Schottky 74LSxx

- TTL Low power 74Lxx TTL Advenced Schottky 74Asxx

- TTL Schottky 74Sxx TTL Advenced Low-power Schottky 74ASLxx

- TTL Fast 74Fxx

Les Circuits CMOS: Série 40xx

- CMOS classique 74Cxx

- CMOS Rapide 74HCxx

- CMOS Rapide 74HCTxx

Notre étude porte sur les deux familles TTL et CMOS afin d'identifier leurs caractéristiques respectives et de les comparer aux données constructeur.

# II. ETUDE PRELIMINAIRE

Rechercher dans le MEMOTECH Electronique© chaque paramètre caractéristique de la technologie des circuits à disposition (1 en TTL, 1 en CMOS) et les organiser dans un tableau.

# III. ETUDE EXPERIMENTALE: FAMILLE TTL

Nous allons utiliser une porte inverseuse (NON) : circuit .......

# III.1 Caractéristique de transfert V<sub>O</sub>(V<sub>I</sub>)

1- A l'aide des données constructeur, tracer le gabarit du diagramme  $V_O(V_I)$ . Faire apparaı̂tre les valeurs  $V_{IH}$ ,  $V_{IL}$ ,  $V_{OL}$ ,  $V_{OH}$  et les plages garanties par le constructeur.

2- <u>Mesures</u>: Tension d'alimentation:  $V_{DD} = 5V$ ;  $V_{SS} = 0V$ Faire varier la tension d'entrée entre 0 et 5V et relever à chaque fois la tension de sortie. Vérifier que la caractéristique s'inscrit dans le gabarit.

# III.2 Caractéristique de sortie $V_O = f(I_O)$

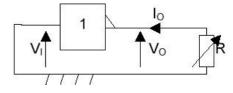

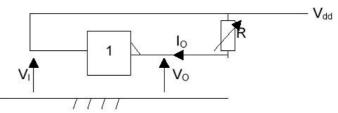

#### III.2.1 Sortie état haut

Faire varier la résistance R. Mesurer VO et IO. Tracer la courbe.

# III.2.2 Sortie état bas

Faire varier la résistance R. Mesurer VO et IO. Tracer la courbe.

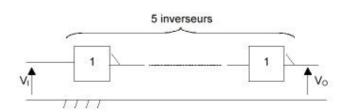

#### III.3 Temps de propagation

Afin de réaliser une meilleure mesure placer cinq inverseurs en cascade.

Le signal  $V_{\rm I}$  est rectangulaire variant entre 0 et 5V. Mesurer les temps de propagation  $t_{\rm PLH}$  et  $t_{\rm PHL}$  et en déduire le temps de propagation moyen  $t_{\rm P}$ .

# IV. ETUDE EXPERIMENTALE: FAMILLE CMOS

Nous allons utiliser une porte NOR câblée en inverseur : circuit .........

# IV.1 Caractéristique de transfert V<sub>O</sub>(V<sub>I</sub>)

Les mesures se font de la même façon que pour les circuits TTL.

# IV.2 Temps de propagation

Placer les quatre inverseurs du boîtier en cascade.

Les mesures se font de la même façon que pour les circuits TTL.

#### V. Conclusion

- 1- Comparer les caractéristique de transferts de chaque technologie.

- 2- Déterminer, en utilisant les données constructeur, les marges de sensibilité aux bruits.

- 3- Une porte TTL peut-elle piloter une porte CMOS, et vice-versa ? Justifier la réponse.

- 4- Comparer les temps de propagation. Que remarque-t-on ?

- 5- Qu'est ce qui déterminera le choix de la technologie à utiliser pour une application donnée ?

- 6- Aurions-nous pu utiliser des circuits TTL standards dans l'objet technique « anti-oubli d'extinction de veilleuses » ? Pourquoi ?